KEYWORDS

Analog-to-digital converter (ADC), class-AB op-amp, delta-sigma modulator, feed forward (FF), successive approximation register (SAR)

논문 리뷰에 들어가기 전에, Keyword 분석을 먼저 정리해 볼게요!

- Analog-to-digital converter (ADC)

[아날로그 공부] Analog to Digital Converter, ADC

[아날로그 공부] Analog to Digital Converter, ADC

ADC 정의 Analog to Digital Converter, ADC는 말 그대로 아날로그 신호를 디지털 신호로 변환하는 회로이다. 표본화(Sampling) → 양자화(Quantization) → 부호화(Encoding) 총 3단계를 통해 아날로그(Analog) 신호

sejinhan-analogic.tistory.com

- class-AB op-amp :

Class-AB 연산 증폭기(Op-Amp)는 전력 효율성과 선형성을 동시에 고려한 증폭기 구조이다. 이는 Class-A와 Class-B 증폭기의 단점을 보완하여, 높은 효율과 낮은 왜곡을 제공하는 방식이다.

- delta-sigma modulator : 입력 신호를 고속 샘플링한 후, 차분, 적분 연산을 조합하여 신호를 변환한다. delta 연산은 입력 신호와 이전 샘플의 차이를 구하는 과정이다. 이를 통해 신호 변화량을 반영하여 양자화 오차를 줄일 수 있다. sigma 연산은 차분 결과를 적분하여 누적하는 과정이다. 이를 통해 신호의 평균값을 유지하고, 잡음을 특정 주파수 대역으로 이동시켜 필터링을 용이하게 만든다.

- feed forward (FF) : 신호 또는 제어 정보를 입력에서 출력으로 직접 전달하는 방식을 의미한다.

- successive approximation register (SAR) : 아날로그 신호를 디지털 신호로 변환할 때, 이진 탐색(Binary Search) 방식으로 순차적으로 근사값을 찾아가는 방식이다.

Abstract

이 논문에서는 2nd order modified feed-forward (FF) delta-sigma modulator을 제안한다. 저전력 소모를 위해 첫 번째 적분기에서 Class-AB OP AMP를 사용하였다. ( Class-AB OP AMP 는 낮은 quiescent current 에서도 slew rate가 향상되는 장점이 있다. ) Quantizer 로는 4bit 비동기식 SAR ADC를 사용하여 전력 소모를 줄였다.

이를 통해 제 안된 ADC는 고해상도와 저전력 특성을 동시에 만족하며 효율적인 ΔΣ ADC 설계를 실현하였다.

INTRODUCTION

이 논문은 저전력 배터리 기반 기기를 위해 전력 소비를 줄인 2차 이산시간 델타-시그마 변조기를 제안하는 내용이다. 입력 피드포워드 구조를 적용하여 루프 필터의 전력 소비를 줄이고, 첫 번째 적분기에 클래스-AB 연산 증폭기를 사용하여 평균 전류 소비를 낮추면서 슬루율을 개선하였다.

제안된 ADC는 1킬로헤르츠 대역폭에서 97.7데시벨의 동적 범위를 달성하며, 소비 전력은 12.3마이크로와트이다. 지연된 피드백을 포함한 수정된 피드포워드 구조를 기반으로 하며, 저전력 및 고해상도 ADC 설계에 적합한 솔루션을 제공한다.

ARCHITECTURE

이 논문에서는 2차 수정된 피드포워드 델타-시그마 모듈레이터를 제안한다. ( 위 그림과 같은 구조이다. )

이 ADC는 두 개의 적분기와 4비트 비동기식 SAR ADC로 구성되며, 패시브 스위치드 커패시터 가산기를 포함한다. 또한, 피드백 경로에 한 클록 주기의 지연을 추가하여 타이밍 제약을 완화하고, 이로 인해 발생할 수 있는 비이상적인 특성을 억제하기 위해 충분한 오버샘플링 비율을 사용한다. 추가적으로, 감산 필터와 안티앨리어싱 필터를 통해 대역 밖 신호를 효과적으로 처리한다. 이 방식은 저전력 및 고해상도 ADC 설계에 유리하다.

CIRCUIT IMPLEMENTATION

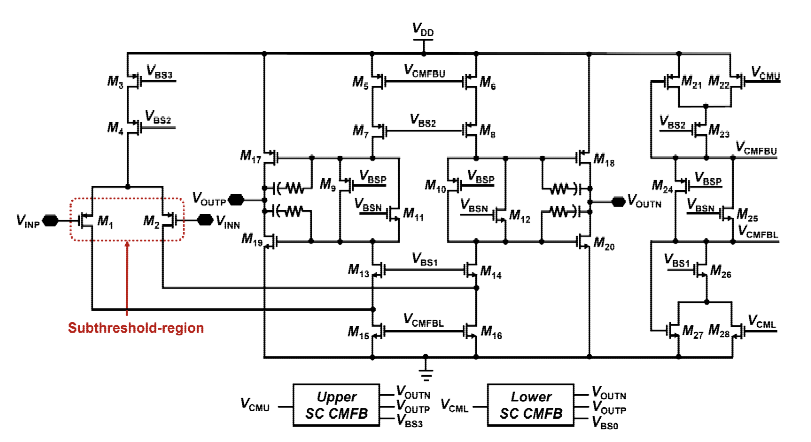

1. Fully Differential Class AB Op-Amp

이 논문에서는 첫 번째 적분기의 6pF 피드백 커패시터와 두 번째 적분기의 500fF 샘플링 커패시터를 효율적으로 구동하기 위해 클래스-AB 연산 증폭기를 사용한다. 클래스-AB 연산 증폭기는 슬루잉 동안 푸시-풀 방식으로 로딩 커패시터를 충전하거나 방전하며, 정해진 전류만을 소모한다. 안정화 기간 동안에는 아주 적은 양의 대기 전류만 소모된다. 클래스-A 연산 증폭기는 슬루잉과 안정화 모두에서 정적 전류를 소모하는데 비해, 클래스-AB 연산 증폭기는 평균 전류 소비를 줄여준다.

이 구조에서 클래스-AB 제어는 'floating class-AB control' 방식을 사용하며, 이를 통해 슬루잉과 안정화 동안 전류를 효율적으로 관리한다. 제어 트랜지스터 MC1, MC2는 MB1-MB4로 구성된 스택된 다이오드 연결 트랜지스터에 의해 바이어스가 제공된다. 이 트랜지스터들은 푸시-풀 동작을 통해 출력 커패시터를 충전하거나 방전시킨다.

또한, 첫 번째 적분기의 두 단계 연산 증폭기는 folded cascode 토폴로지를 사용하여 충분한 DC 이득을 얻으며, 입력 PMOS 장치들은 서브 임계 영역에서 작동하여 좋은 노이즈 성능을 제공한다. 이때 클래스-AB 제어 트랜지스터들의 노이즈와 오프셋은 첫 번째 단계 연산 증폭기의 합산 회로에 배치하여 완화된다.

이 설계에서는 전통적인 각 단계별 CMFB(Common-Mode Feedback) 대신, 글로벌 피드백 루프를 통해 출력 공통모드를 조정한다. 이 글로벌 루프 CMFB는 두 개의 공통모드 제어 경로를 통해 출력 공통 모드를 조정하는 전압을 생성하며, 이를 통해 안정적인 공통모드 출력을 유지한다.

마지막으로 출력 공통 모드를 안정화시키기 위해 이득이 -1/3인 인버팅 증폭기를 사용하여 트랜지스터들의 변환전도비(g)가 조정된다. 이 방식은 출력 공통 모드가 안정적으로 수렴하도록 도와준다.

2. Loop Filter

첫 번째 적분기에서의 Loop filter 구조는 위 그림과 같다. 첫 번째 적분기에서는 부스트래핑 스위치와 초퍼 안정화 기법을 사용하여 선형성과 잡음을 개선하고, 클래스-AB 연산 증폭기를 사용해 전력 효율을 높인다.

- Gate Bootstrapping Switch 원리

: 스위치를 이용한 샘플링 네트워크에서 주로 발생하는 비선형성 문제는 스위칭 전압 강하이다. 일반적으로 스위치가 켜졌을 때 드레인과 소스 간에 일정한 전압 강하가 발생하는데 이로 인해 샘플링 정확도가 떨어지고 전압의 왜곡이 발생하는 문제는 비선형 특성을 유발한다.

Bootstrapping Switch는 스위치가 켜질 때 커패시터를 통해 스위치의 드레인-소스 전압을 증가시킨다. 이로 인해 스위치의 전압 강하를 줄여 전압 왜곡이 최소화되어 스위치가 비선형 영역에서 동작하지 않도록 한다.

- 전압 왜곡이 비선형성인 이유

: 전압과 전류 간의 관계가 선형적이지 않기 때문이다. 즉, 이상적인 경우 전압과 전류는 비례해야 하지만, 실제 회로에서 전압 왜곡이 발생하면 전압과 전류 간의 관계가 비례하지 않고 비선형적으로 변하게 된다.

번째 적분기에서의 Loop filter 구조는 위 그림과 같다. 이 적분기는 첫 번째 적분기에서 나온 출력을 샘플링하여 처리하는데, f2 단계에서 샘플링이 이루어지고, f1 단계에서는 지연 없이 적분이 된다. 두 번째 적분기에서 사용되는 커패시터는 피드백 커패시터 CF2 (250fF)와 퀀타이저의 샘플링 커패시터 (80fF)인데, 이러한 낮은 용량을 고려했을 때, 클래스-AB 연산 증폭기를 사용하는 것은 비효율적이다. (클래스-AB 연산 증폭기는 추가적인 바이어스 회로와 제어 회로를 요구하기 때문 대이다.) 따라서, 더 간단하고 효율적인 folded-cascode 연산 증폭기를 사용한다. 이 방식은 구조가 간단하고 전력 소비를 최소화할 수 있는 장점이 있다.

3. 4-Bit Asynchronouis SAR ADC

SAR ADC는 Successive Approximation Register (SAR) 방식을 사용하는 ADC이다. 이 방식은 입력 신호를 샘플링하고, 그 신호와 비교할 수 있는 디지털 값을 찾는 방식이다. SAR ADC는 다음과 같은 주요 구성 요소로 이루어져 있습니다.

(1) CDAC (Capacitive Digital-to-Analog Converter): SAR ADC에서 아날로그 신호를 디지털 값으로 변환하는 역할을 한다.

(2) 비교기 (Comparator): 디지털 값과 아날로그 신호를 비교하여 SAR 알고리즘을 통해 결정된 값을 기반으로 변환 작업을 수행한다.

(3) 제어 로직 (Control Logic): ADC의 동작을 제어하며 SAR 알고리즘을 구현합니다.

위 그림은 PMOS 입력 래치 비교기의 회로를 나타낸다. 비교기는 입력 공통 모드 전압이 VDD/2보다 낮은 경우에도 잘 작동하도록 설계되었으며, ( SAR ADC에서 비교기의 입력 공통 모드 전압이 VDD/2보다 낮기 때문에 PMOS 입력 래치 비교기가 사용된다.) PMOS 입력 비교기는 SAR ADC의 성능을 향상시키기 위해 사용되며, 낮은 전압에서 안정적인 동작을 보

장한다. 이 비교기는 CDAC에서 나온 아날로그 신호를 샘플링하여 디지털 값으로 변환할 수 있도록 해준다.

CONCLUSION

이 논문은 2차 디지털 델타-시그마 변조기를 제시한다. 제안된 ADC는 루프 필터의 충분한 타이밍 여유를 위해 수정된 FF 구조를 사용하며 지연된 피드백을 채택한다. 첫 번째 적분기에 빠른 슬루잉과 낮은 정적 전류를 달성하기 위해 플로팅 클래스-AB 제어가 적용된 클래스-AB 연산 증폭기가 사용된다. 이 ADC는 28nm CMOS 공정으로 제작되었으며, 1kHz 신호 대역폭에서 97.7dB의 동적 범위(DR)와 94.8dB의 피크 신호-잡음 왜곡비(SNDR)를 달성하며, 소비 전력은 12.3μW이다.